# pLUTo: Enabling Massively Parallel Computation in DRAM via Lookup Tables

| João Dinis Ferreira <sup>§</sup> |            | Gabriel Falcao <sup>†</sup> |                   | Juan Góm     | ez-Luna <sup>§</sup> | Mohammed Alser§         |                    |

|----------------------------------|------------|-----------------------------|-------------------|--------------|----------------------|-------------------------|--------------------|

| Lois Orosa <sup>§</sup> ∇        | Mc         | hammad Sadrosad             | lati <sup>§</sup> | Jeremie      | S. Kim <sup>§</sup>  | Geraldo F. Oli          | veira <sup>§</sup> |

|                                  | Tah        | a Shahroodi <sup>‡</sup>    | Anan              | t Nori*      | Onur Mutlu           | §                       |                    |

| §ETH Zürich                      | †IT, Unive | ersity of Coimbra           | $\nabla Gali$     | icia Superco | omputing Cente       | r <sup>‡</sup> TU Delft | *Intel             |

Data movement between the main memory and the processor is a key contributor to execution time and energy consumption in memory-intensive applications. This data movement bottleneck can be alleviated using Processing-in-Memory (PiM). One category of PiM is Processing-using-Memory (PuM), in which computation takes place inside the memory array by exploiting intrinsic analog properties of the memory device. PuM yields high performance and energy efficiency, but existing PuM techniques support a limited range of operations. As a result, current PuM architectures cannot efficiently perform some complex operations (e.g., multiplication, division, exponentiation) without large increases in chip area and design complexity.

To overcome these limitations of existing PuM architectures, we introduce **pLUTo** (*processing-using-memory with lookup table* (*LUT*) *operations*), a DRAM-based PuM architecture that leverages the high storage density of DRAM to enable the massively parallel storing and querying of lookup tables (LUTs). The key idea of pLUTo is to replace complex operations with low-cost, bulk memory reads (i.e., LUT queries) instead of relying on complex extra logic.

We evaluate pLUTo across 11 real-world workloads that showcase the limitations of prior PuM approaches and show that our solution outperforms optimized CPU and GPU baselines by an average of 713× and 1.2×, respectively, while simultaneously reducing energy consumption by an average of 1855× and 39.5×. Across these workloads, pLUTo outperforms state-of-the-art PiM architectures by an average of 18.3×. We also show that different versions of pLUTo provide different levels of flexibility and performance at different additional DRAM area overheads (between 10.2% and 23.1%). pLUTo's source code and all scripts required to reproduce the results of this paper are openly and fully available at https://github.com/CMU-SAFARI/pLUTo.

# 1. Introduction

*Processing-in-Memory* (PiM) is a promising paradigm that augments a system's memory with compute capability [1–5] to alleviate the *data movement bottleneck* between processing and memory units [2, 6–17]. PiM architectures can be classified into two categories [1, 18]: 1) **Processing-near-Memory (PnM)**, where computation takes place in dedicated processing elements (e.g., accelerators [11, 19–43], processing cores [11, 30–32, 41, 44–58], reconfigurable logic [59–63]) placed near the memory array (e.g., [11, 19–41, 44–67]), and 2) **Processing-using-Memory (PuM)**, where computation takes place *inside* the memory array by exploiting intrinsic analog operational properties of the memory device (e.g., [41, 55, 68–91]).

In DRAM-based PnM, data is transferred from the DRAM array to nearby processors or specialized accelerators, which could be 1) part of the DRAM chip, but separate from the DRAM array [22, 36-38, 42, 43, 51-54, 56, 58], e.g., near the DRAM banks, 2) integrated into the logic layer of 3D-stacked memories [11, 20, 21, 23-25, 28-32, 34, 39, 44-50, 55, 57, 59, 60, 66, 67], or 3) inside the memory controller [35, 92, 93]. PnM enables the design of flexible substrates that support a diverse range of operations. However, the performance, efficiency, and scalability of near-bank PnM architectures [22, 36-38, 42, 43, 51–54, 56, 58] can be limited by design and fabrication challenges, such as 1) the difficulty in designing complex logic due to the limited number of DRAM metal layers [94, 95], and 2) the inefficiency of the DRAM process for the implementation of digital logic due to its heavy optimization for memory density [51, 54]. In 3D-stacked memories, the logic layer's limited area and thermal budgets impose additional constraints. All these design and fabrication issues lead to generally very simple PnM execution engines, which are unable to exploit the entire DRAM bandwidth [15, 47, 54].

In contrast, PuM architectures enable computation *within* the memory array. The key benefit of PuM architectures is that *data does not leave the memory array during computation.* As a result, PuM architectures can provide high compute throughput by performing operations in a bulk parallel manner, often at the granularity of memory rows. Prior PuM works [70, 72, 74, 75, 79, 82, 84, 96, 97] propose mechanisms for the execution of bulk bitwise operations (e.g., bitwise MAJority, AND, OR, NOT) [72, 74, 78, 80, 82–85, 87, 91, 98] and bulk arithmetic operations [70, 75, 79, 96, 97]. However, these proposals have two important limitations: 1) the execution of some complex operations (e.g., multiplication, division) incurs high latency and energy consumption [75], and 2) other complex operations (e.g., exponentiation, trigonometric functions) are not even supported.

We aim to overcome these two limitations of prior PuM architectures in this work. To this end, we employ *LUT-based computing*, i.e., the use of memory read operations (*LUT queries*) to retrieve the results of complex operations from lookup tables that hold precomputed values. Concretely, a *LUT query* is a *memory read operation* that, for a given input value *x*, returns f(x), i.e., the result of applying some function *f* to the input *x*. Many PuM architectures [96, 97, 99] exploit LUT-based computing to improve the performance of a few complex operations. However, *no* prior work supports the general-purpose execution of LUT-based complex operations.

Our goal in this work is to extend the functionality of DRAMbased PuM systems to provide support for general-purpose execution of complex operations. To this end, we propose pLUTo: processing-using-memory with lookup table (LUT) operations, a DRAM-based PuM architecture that leverages LUT-based computing via bulk querying of LUTs to perform complex operations beyond the scope of prior DRAM-based PuM proposals. pLUTo introduces a novel LUT-querying mechanism, the *pLUTo LUT Query*, which enables the simultaneous querying of multiple LUTs stored in a single DRAM subarray. In pLUTo, the number of elements stored in each LUT may be as large as the number of rows in each DRAM subarray (e.g., 512–1024 rows [100–102]). pLUTo requires the following two modest modifications to DRAM hardware: 1) row sweeping *logic*, which enables the *sweeping* of DRAM rows, i.e., the successive activation of consecutive rows in a DRAM subarray; 2) match logic, which identifies matches between the elements in the input row and the *index* of the currently active row in the subarray that holds multiple copies of one or more LUTs. We describe three pLUTo designs: pLUTo-BSA (Buffered Sense Amplifier), pLUTo-GSA (Gated Sense Amplifier), and pLUTo-GMC (Gated Memory Cell). These designs achieve different performance, energy efficiency, and area overhead trade-offs.

To enable the seamless integration of pLUTo with the system, we methodically describe the changes that allow programmers to offload their applications to pLUTo. These changes comprise 1) pLUTo ISA instructions that enable support for each of the DRAM operations required for pLUTo's operation, 2) the pLUTo Library, an API library that includes routines that programmers can use to conveniently express pLUTo operations at a high level of abstraction, 3) the pLUTo Compiler, which analyzes an application's data dependency graph to plan the in-memory placement and alignment of data, and 4) the pLUTo Controller, a modified memory controller that supports the execution of pLUTo ISA instructions.

We evaluate pLUTo on a diverse range of real-world arithmetic, bitwise logic, cryptographic, image processing, and neural network workloads that demonstrate the limitations of existing PuM architectures and how pLUTo is able to overcome them. These workloads include 1) bitwise (AND/OR/XOR), arithmetic (addition, multiplication), and nonlinear operations (substitution tables, image binarization, and color grading); and 2) a quantized neural network. We compare pLUTo to state-of-the-art processor-centric architectures (CPU [103], GPU [104], FPGA [105]) and PiM architectures (PnM [67], PuM [75, 79, 84]). Our evaluations show that pLUTo consistently and considerably outperforms these five baselines in performance and energy consumption.

We make the following key contributions:

- We introduce pLUTo, a new DRAM-based PuM architecture that introduces support for general-purpose operations through the use of bulk lookup table (LUT) queries.

- We propose three different and new pLUTo designs with varying trade-offs in performance, energy efficiency, and DRAM area overhead.

- We describe the end-to-end system integration of pLUTo, including 1) ISA instructions, 2) an API library, 3) a compiler, and 4) modifications to the memory controller.

- We experimentally demonstrate that pLUTosignificantly outperforms CPU [103], GPU [104], FPGA [105], and PiM [67, 75, 79, 84] baselines across a wide variety of real-world bitwise logic, arithmetic, cryptographic, image processing, and neural network workloads.

- We open-source pLUTo's source code and all scripts required to reproduce the results presented in this paper on https://github.com/CMU-SAFARI/pLUTo.

## 2. Background

This section describes the hierarchical organization of DRAM and provides an overview of relevant prior work we build on. We refer the reader to prior work [79, 84, 100, 106–108] for more detailed descriptions of DRAM operation.

#### 2.1. DRAM Background

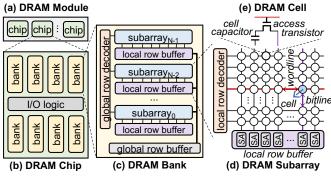

DRAM is organized hierarchically: each DRAM module consists of multiple chips, banks, and subarrays, as Figure 1 shows. A DRAM module (Figure 1a) consists of multiple DRAM chips (Figure 1b), each of which contains multiple DRAM banks (e.g., 8 for DDR3 [109], 16 for DDR4 [110]) and I/O logic. Each DRAM bank (Figure 1c) is divided into DRAM subarrays [100] (Figure 1d), which are two-dimensional arrays of DRAM cells (Figure 1e). DRAM subarrays in a bank share peripheral circuitry (e.g., a global row decoder and a global row buffer). Each DRAM cell contains one cell capacitor and one access transistor. The cell capacitor encodes a single bit as stored electrical charge. The access transistor connects the cell capacitor to the bitline wire. Each bitline is shared by all DRAM cells in a column and is connected to a sense amplifier (SA in Figure 1d). The set of sense amplifiers in a subarray makes up the local row buffer.

Figure 1: Internal organization of a DRAM module.

Reading and writing data in DRAM occurs over three phases. 1) Row Activation. The memory controller initiates a memory request by issuing an activate (ACT) command together with a DRAM row address to the target DRAM bank. Once the DRAM chip receives the ACT command, it asserts the corresponding wordline to activate the DRAM row. The row activation process happens in three main steps. First, the wordline of the accessed row is driven with high voltage, turning on the row's access transistors and creating a path for charge sharing between each DRAM cell and its bitline. This process induces a voltage fluctuation,  $\pm \delta$ , that affects the voltage level of the *precharged* (i.e., set to  $V_{DD}/2$ ) bitline. If the cell is charged, the bitline voltage becomes  $V_{DD}/2 + \delta$ . Otherwise, it becomes  $V_{DD}/2 - \delta$ . Second, each sense amplifier in the local row buffer amplifies its bitline's voltage fluctuation  $(\pm \delta)$  until the bitline voltage reaches either  $V_{DD}$  or 0. Third, the original voltage level of each cell capacitor in the activated row is restored, since each access transistor allows charge to flow between each bitline and each corresponding DRAM cell in the activated row. Once the row activation process is complete, the local row buffer contains the values originally stored in the cells along the asserted wordline. 2) Reading/Writing. The memory controller issues read (RD) or write (WR) commands together with a DRAM column address to read or write chunks of the data latched in the local row buffer. In the case of a read, data in the corresponding columns is sent to the CPU through the DRAM's I/O circuitry and the memory bus. In the case of a write, data received from the CPU modifies the corresponding columns' bitline (and thus cell) voltages.

3) Precharging. The memory controller issues a precharge (PRE) command to free up the local row buffer and allow the activation of other DRAM rows. To achieve this, the wordline is de-asserted, which turns off the access transistors along a DRAM row, and the subarray's bitlines are precharged (i.e., restored to  $V_{DD}/2$ ).

#### 2.2. Enhanced DRAM Architectures

pLUTo optimizes key operations by incorporating the following previous proposals for enhanced DRAM architectures.

**Intra-Subarray Data Copy.** The *RowClone-FPM* (<u>F</u>ast <u>Parallel Mode</u>) [81] operation enables data to be copied between two DRAM rows belonging to the same DRAM subarray. This is achieved via two consecutive activations: first to the source row, then to the destination row. Doing so asserts the destination row's wordline while the contents of the source row are already in the subarray's row buffer, which causes the entire row buffer's contents to be written to the destination row.

**Inter-Subarray Data Copy.** The *LISA-RBM* (Row Buffer Movement) operation [108] copies the contents of one local row buffer to another local row buffer in a different subarray in the same bank without relying on the external memory channel. This is achieved by linking neighboring subarrays with isolation transistors.

**Subarray-Level Parallelism.** *MASA* [100] is a mechanism that enables subarray-level parallelism by overlapping the latency of memory accesses directed to different subarrays' bitlines. MASA enables multiple rows in different subarrays to be activated and to be accessed (read or written to) in parallel.

**Bulk Bitwise Operations.** *Ambit* [84] is a PuM architecture that introduces native support for bulk bitwise logic operations (MAJority, AND, OR, NOT) between rows in a DRAM subarray. Ambit uses the *triple row activation* primitive (which concurrently asserts three wordlines, leading to the execution of the majority function between the contents of three DRAM rows)

and the copy operation enabled by RowClone [81] to enable these simple, row-granularity bitwise operations.

**Shifting.** *DRISA* [79] is a PuM architecture that features support for intra-row shifting in DRAM. Using this mechanism, the contents of a DRAM row can be shifted by 1 or 8 bits at a time, at the cost of *one* ACT-ACT-PRE [84] command sequence.

# 3. Motivation

Our goal in this work is to extend the functionality of Processingusing-Memory (PuM) architectures to provide support for the general-purpose execution of complex operations. In particular, pLUTo is motivated by the following two key observations. First, state-of-the-art PuM architectures [41, 55, 68-91, 96] provide very high performance and energy efficiency by mitigating data movement, but they only support a limited range of operations. For example, prior DRAM-based PuM accelerators only support the execution of basic operations (e.g., bitwise logic, addition) [70, 74, 75, 79, 82, 84, 96, 97] or require long sequences of DRAM commands to support more complex operations (e.g., multiplication, division) [75]. Second, lookup tables (LUTs) enable the replacement of complex computations with cheaper LUT query operations (i.e., memory reads). pLUTo improves prior PuM works by leveraging their best features (i.e., high parallelism, reduced data movement) and addressing their main drawbacks (i.e., reduced range of supported operations and low performance for complex operations). We achieve this via the introduction of the *pLUTo LUT Query* operation (described in Section 4.1), which enables the bulk querying of all the values in a given input DRAM row.

#### 4. An Overview of pLUTo

The key contribution of pLUTo is the *pLUTo LUT Query*, an operation that enables the bulk execution of a large number of LUT queries *inside* a DRAM subarray. Each individual *LUT query* is defined as a *memory read operation* that, given an *input value x*, returns as its *output value* the result of applying some arbitrary function f to x, i.e., f(x). Building on the pLUTo LUT Query, pLUTo employs *LUT-based computing* (i.e., *the replacement of complex operations with equivalent LUT queries*) to perform computation under the Processing-using-Memory paradigm. LUT-based computing requires that each complex operation to be replaced with a LUT query be *deterministic*; in other words, the behavior of the function f being replaced with a LUT query *should only depend on its input value x*. The construction of a LUT requires a one-time effort of computing all its values, i.e., all *LUT elements*.

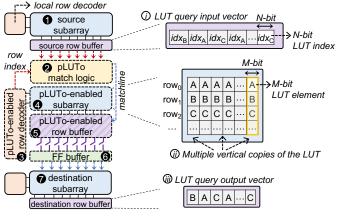

Figure 2 shows an overview of the DRAM structures required to perform a *pLUTo LUT Query*.<sup>1</sup> First, the *source subarray* (1) in Figure 2) stores the *LUT query input vector* ((i) in Figure 2), which consists of a set of *N*-bit LUT indices associated with LUT elements. Second, the *pLUTo Match Logic* (2) comprises a set of comparators that identify matches between

<sup>&</sup>lt;sup>1</sup> Figure 2 assumes that pLUTo has been implemented with the pLUTo-BSA design (described in Section 5.1). However, the key ideas of the pLUTo LUT Query described in this section apply to all three pLUTo designs described in Sections 5.1 to 5.3.

1) the row index of the currently activated row in the pLUToenabled subarray, and 2) each LUT index in the LUT query input vector (i.e., the source subarray's row buffer). Third, the pLUTo-enabled row decoder (3) enables the successive activation of consecutive DRAM rows in the pLUTo-enabled subarray with a single DRAM command. It also outputs the row index of the currently activated row as input to the pLUTo Match Logic. Fourth, the *pLUTo-enabled subarray* (4) stores multiple vertical copies of a given LUT ((ii)), which consists of *M*-bit LUT elements. Fifth, the *pLUTo-enabled row buffer* (5) allows the reading of individual LUT elements from the activated row in the *pLUTo-enabled subarray*. This is possible by extending the DRAM sense amplifier design of the pLUTo-enabled row buffer with switches controlled by the pLUTo Match Logic (using the *matchline* signal). Sixth, the *flip-flip* (*FF*) *buffer* (6) enables pLUTo to temporarily store select LUT elements by copying them from the pLUTo-enabled row buffer, conditioned on the output of the pLUTo Match Logic following each row activation. Seventh, a LISA-RBM operation copies the entire contents of the FF buffer (i.e., the LUT query output vector, (iii)) into the destination row buffer, i.e., the row buffer of the *destination subarray* (7).

Figure 2: Main components of pLUTo.

In contrast to the bit-serial paradigm employed by prior PuM architectures (e.g., SIMDRAM [75]), pLUTo operates in a *bit-parallel* manner; in other words, the bits that make up each LUT element (e.g., A) are stored *horizontally* (i.e., in adjacent bitlines), and all the copies of each LUT element (i.e., {A,A,...,A}) take up *one whole row* in the depicted pLUTo-enabled subarray ((ii)).<sup>2</sup>

## 4.1. The pLUTo LUT Query

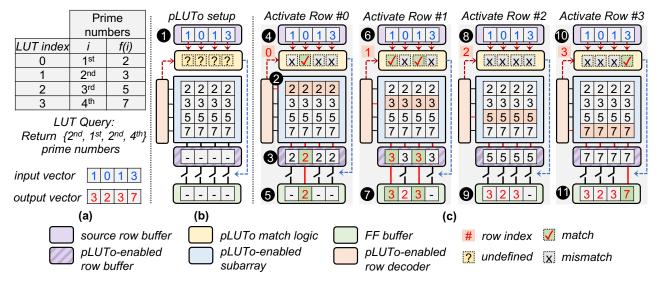

The pLUTo LUT Query enables all the elements stored in a source row buffer to simultaneously be used to query a LUT. We illustrate the pLUTo LUT Query using a simple example that employs a small LUT to store the first four prime numbers (i.e., {2,3,5,7}) at LUT indices {0,1,2,3}, as shown in Figure 3a.

In our example, the user-defined LUT query will return the  $\{2^{nd}, 1^{st}, 2^{nd}, 4^{th}\}$  prime numbers, which corresponds to a LUT query input vector [1,0,1,3] and an expected LUT query output vector [3,2,3,7] (i.e.,  $\{2^{nd}, 1^{st}, 2^{nd}, 4^{th}\}$  prime numbers  $\Rightarrow$  {LUT[1],LUT[0],LUT[1],LUT[3]} = {3,2,3,7}). Note that, in this example, *four* individual lookup operations are performed by a *single* pLUTo LUT Query.

Four copies of this LUT are stored in a pLUTo-enabled subarray, as shown in Figure 3b: each row *i* contains repeated copies of the element corresponding to the entry at the *i*-th index of the LUT. pLUTo performs the pLUTo LUT Queryoperation in five steps. First, the memory controller loads the LUT query input vector from the source subarray (not shown) into the source row buffer (1) in Figure 3). Second, the memory controller issues a pLUTo Row Sweep operation (Section 5.1.1) to consecutively activate all four rows in the pLUTo-enabled subarray that hold LUT elements, in order (i.e., the row indices to be activated are {#0,#1,#2,#3}). After each row activation during a pLUTo Row Sweep operation, the pLUTo Match Logic identifies matches between 1) the row index of the currently activated row in the pLUTo-enabled subarray, and 2) each element of the LUT query input vector (i.e., the source row buffer). The aim of this procedure is to *allow* for consecutive LUT elements, in turn, to be copied to the FF buffer, if they are part of the final output row for the ongoing pLUTo LUT Queryoperation. Consider the activation of row #0(2), which creates four copies of LUT[0] (i.e., the LUT element with the value 2) in the pLUTo-enabled row buffer (3). Concurrently with this row activation, the pLUTo Match Logic 1) identifies a match between the index of the currently activated row (#0) and the second LUT index in the LUT query input vector (4), and 2) asserts the matchlines corresponding to the second element in the pLUTo-enabled row buffer. As a result, the switch at the second LUT element in the pLUTo-enabled row buffer is closed, enabling the LUT element to be copied to the *second position in the FF buffer* (5).

Third, the activation of row index #1 illustrates how multiple LUT indices may be matched at once: in this case, the LUT element of LUT[1] is required by *both the first and the third* positions of the LUT query input vector ( $\bigcirc$ ). Therefore, the pLUTo Match Logic asserts the matchlines corresponding to *both the first and third* LUT elements, which copies both LUT elements into the FF buffer ( $\bigcirc$ ). Fourth, the pLUTo LUT Query operation progresses by activating row #2, which produces *no* matches with LUT indices stored in the LUT Query input vector ( $\bigcirc$ ). Fifth, when activating row #3, the pLUTo Match Logic identifies a match between row index #1 and the *fourth* element of the LUT query input vector ( $\bigcirc$ ), which leads to the copy of the LUT element LUT[3] (i.e., 7) into the *fourth* position in the FF buffer ( $\bigcirc$ ).

At this point, the pLUTo Row Sweep operation has been completed, and the FF buffer holds the results of the pLUTo LUT Query. The contents of the FF buffer are then copied to the *destination row buffer* (not shown in Figure 3) using a LISA-RBM command (see Section 2.2).

<sup>&</sup>lt;sup>2</sup> Throughout this example, we assume that all  $\{A, B, C, \ldots\}$  values are 8 bits wide, although this bit width is a parameter of each pLUTo LUT Query and may vary (see Section 6.2).

Figure 3: A pLUTo LUT Query: (a) a LUT containing the first four prime numbers and an example user-specified LUT query, (b) setup of pLUTo's main components prior to the execution of the pLUTo LUT Query, and (c) steps of the pLUTo LUT Query. This pLUTo LUT Query returns into the destination row buffer (not depicted) the i-th prime number for each LUT index in the source row buffer.

#### 5. pLUTo's Hardware Design

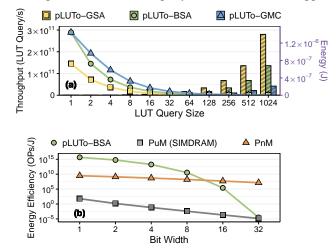

This section describes the hardware design of pLUTo that enables the pLUTo LUT Query operation. First, we propose three different pLUTo architectures. Each of these architectures provides a different trade-off between performance, energy efficiency, and area overhead: 1) pLUTo-BSA (<u>Buffered Sense</u> <u>Amplifier</u>)incurs moderate hardware overhead and provides intermediate performance and energy efficiency gains; 2) pLUTo-GSA (<u>Gated Sense Amplifier</u>)incurs the lowest hardware overhead but provides the lowest performance and energy efficiency; 3) pLUTo-GMC (<u>Gated Memory Cell</u>)incurs the highest hardware overhead but provides the highest performance and energy efficiency. Second, we describe the synergistic integration of the novel components of pLUTo with prior PuM-based operations [79, 84, 108] and subarray-level parallelism [100].

# 5.1. pLUTo-BSA (<u>Buffered Sense Amplifier</u>) Design

To enhance a DRAM subarray with support for the execution of pLUTo LUT Queries, we modify the DRAM subarray's row decoder and local row buffer to implement the *pLUTo Match Logic*. Uniquely, pLUTo-BSA employs the *key idea* of relying on a secondary row buffer (the *FF buffer*, see Section 5.1.3) to store matching LUT elements during a pLUTo Row Sweep.

**5.1.1. pLUTo-Enabled Row Decoder.** The pLUTo-enabled row decoder enhances the DRAM row decoder by introducing support for the *pLUTo Row Sweep* operation. The pLUTo Row Sweep extends the self-refresh operation (already present in commodity DRAM [111–113]) to activate consecutive rows quickly. With support for the pLUTo Row Sweep operation, pLUToactivates all the rows in the pLUTo-enabled subarray that store LUT elements during a pLUTo LUT Query operation *via a single new DRAM command.* The latency of the pLUTo Row Sweep is equal to  $(tRCD + tRP) \times LUT_{\#Elems}$ , where tRCD ( $\approx 12.5$  ns in DDR4 [110]) is the time that must elapse to ensure that the sense amplifiers can reliably amplify the voltage perturbation on the bitline, tRP ( $\approx 12.5$  ns in DDR4 [110]) is the

time that must elapse between a PRE command and the next ACT command, and  $LUT_{\#Elems}$  is the total number of rows swept.

**5.1.2. pLUTo Match Logic.** As shown in Figure 2a, we implement the *pLUTo Match Logic* between the source subarray and the pLUTo-enabled subarray. This logic comprises a set of *comparators*; there are as many comparators in the pLUTo Match Logic as there are *elements* in the source row buffer. Every *i*-th comparator in the pLUTo Match Logic receives as input the following two *N*-bit values, where *N* is *the bit width of each LUT element:* 1) the row index of the currently activated row in the pLUTo-enabled subarray, and 2) the *i*-th element in the source subarray's row buffer. Each comparator outputs an *N*-bit value (the *matchlines* in pLUTo's design) that depends on the result of the comparison between its two *N*-bit inputs: if the two inputs exactly match, all *N* matchlines at the output are driven high; otherwise, all matchlines are driven low.

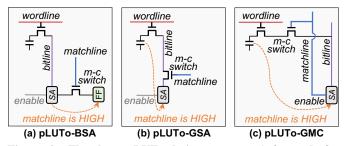

5.1.3. pLUTo-Enabled Row Buffer. Performing the pLUTo LUT Queryoperation as described in Section 4.1 requires a mechanism to perform many fine-grained (i.e., LUT-elementwise) operations throughout a pLUTo Row Sweep, to both 1) read data from the row buffer of the pLUTo-enabled subarray, and 2) write the result of the pLUTo LUT Query operation to some output buffer. To realize this functionality, which commodity DRAM does not support, we connect one flip-flop (FF) to every sense amplifier in the pLUTo-enabled row buffer using a matchline-controlled switch (m-c switch, shown in Figure 4a). Each m-c switch is closed only if there is a match between the row index of the currently activated row in the pLUTo-enabled subarray and the corresponding LUT index in the LUT Query input vector. The complete row of FFs constitutes an FF buffer, which gives pLUTo-BSA (Buffered Sense Amplifier) its name. In this design, when a sense amplifier reads a DRAM cell's value, this value is also immediately written into the corresponding FF, but only if the corresponding *matchline* signal is high (i.e., if the m-c switch connected to the FF is closed).

Figure 4: The three pLUTo designs. *m-c switch* stands for matchline-controlled switch. Orange-dashed lines show how charge flows in case the matchline signal is asserted.

**5.1.4. Analysis of pLUTo-BSA.** pLUTo-BSA's design entails the following pLUTo LUT Query throughput, pLUTo LUT Query energy consumption, and area overhead values:

• *Throughput:* pLUTo-BSA's maximum pLUTo LUT Query throughput (in *number of LUT queries per second*, LUTs/s) for a single pLUTo-enabled subarray depends on the number of LUT indices that fit in the source subarray  $\left(\frac{RowSize_{bytes}}{LUT_{ElementSize}}\right)$  and the latency of a pLUTo Row Sweep ((tRCD + tRP) ×  $LUT_{#Elems}$ ). Thus, pLUTo-BSA's maximum throughput is

$$BSA_{Throughput} = \frac{RowSize_{bits}/input_{bit width}}{(tRCD + tRP) \times LUT_{#Elems}} LUTs/s.$$

• *Energy Consumption:* The energy pLUTo-BSA consumes during a pLUTo Row Sweepdepends on the energy consumed by each DRAM row activation/precharge and *LUT*<sub>#Elems</sub>, the total number of rows swept in the pLUTo-enabled subarray:

$$BSA_{Energy} = (E_{RCD} + E_{RP}) \times LUT_{\#Elems}$$

Area Overhead: The area overhead of pLUTo-BSA includes the area of the pLUTo Match Logic (*RowSize<sub>bytes</sub> × Area<sub>ByteComp</sub>*), matchline-controlled switches (*RowSize<sub>bits</sub> × Area<sub>m-c switch</sub>*), and FF buffer (*RowSize<sub>bits</sub> × Area<sub>FF</sub>*). Thus, pLUTo-BSA's area overhead is

$BSA_{Area} = RowSize_{bytes} \times Area_{ByteComp} + RowSize_{bits} \times Area_{m-c \ switch} + RowSize_{bits} \times Area_{FF}.$

#### 5.2. pLUTo-GSA (Gated Sense Amplifier) Design

*pLUTo-GSA* differs from pLUTo-BSA in its pLUTo-enabled row buffer design and in its implementation of the pLUTo Row Sweepoperation. pLUTo-GSA's *key idea* is to use the sense amplifier as a buffer that stores *only* the LUT elements indicated as a match by the pLUTo Match Logic. By doing this, pLUTo-GSA eliminates the need for a secondary buffer (such as the FF buffer in pLUTo-BSA) to store LUT elements during a pLUTo Row Sweepoperation. pLUTo-GSA provides reduced area overhead over pLUTo-BSA, at the expense of reduced throughput and energy efficiency.

**5.2.1. pLUTo-GSA Row Buffer.** Each sense amplifier in pLUTo-GSA's row buffer is *gated* from its bitline by a matchline-controlled switch (Figure 4b). This switch (i.e., isolation transistor) incurs a lower area overhead than the FF buffer used by pLUTo-BSA, resulting in pLUTo-GSA's higher area efficiency. During a pLUTo LUT Query, if the matchline signal is high (i.e., the switch is closed), the sense amplifier is electrically

connected to its bitline, thus amplifying bitline voltage perturbations normally. However, if the matchline signal is low (i.e., the switch is open), the sense amplifier does *not* respond to the perturbation induced by its corresponding DRAM cell, which leads to the loss of the cell's contents during row activation (i.e., implementing pLUTo-GSA's row buffer leads to destructive reads). This represents a potential for LUT data loss, which means that *a LUT must be loaded into the pLUTo-enabled subarray before every pLUTo LUT Query in pLUTo-GSA*, leading to performance overheads compared to pLUTo-BSA.

5.2.2. The pLUTo Row Sweep. The latency of the pLUTo Row Sweep operation is lower in pLUTo-GSA than in pLUTo-BSA. This is because 1) row activations in pLUTo-GSA's pLUTo Row Sweep do not require the full-fledged activation process required to read DRAM data, but only the triggering of the charge sharing process, and 2) the pLUTo Row Sweep does not require a precharge (PRE) command to be issued after every activate (ACT) command, since each unmatched bitline remains in a precharged state (i.e., the voltage in each bitline remains at  $V_{DD}/2$  until the pLUTo Match Logic registers a match. Instead, a single PRE command may be issued at the end of the pLUTo Row Sweep. However, row activations in pLUTo-GSA's pLUTo Row Sweep lead to LUT data loss for unmatched elements: when an unmatched DRAM cell capacitor is discharged, its charge level will *not* be restored since the matchline-controlled switch leaves the path between the bitline and the sense amplifier open.

The total time required to perform a pLUTo Row Sweep in pLUTo-GSA is equal to tRCD  $\times N$  + tRP, where tRCD ( $\approx 12.5$  ns in DDR4 [110]) is the time that must elapse between the DRAM chip receiving an ACT command and the sense amplifier finishing sensing the voltage perturbation in the bitline, tRP ( $\approx 12.5$  ns in DDR4 [110]) is the precharge time, and  $LUT_{\#Elems}$  is the total number of rows swept. This is about half the time a pLUTo Row Sweep requires in pLUTo-BSA.<sup>3</sup> However, due to the destruction of row contents during the pLUTo Row Sweep, the calculation of the average latency of a pLUTo LUT Query in pLUTo-GSA must also factor in the latency of loading data into a pLUTo-enabled subarray before every pLUTo Row Sweep  $(LISA_{RBM} \times LUT_{\#Elems})$ . As a result, while the latency of the pLUTo Row Sweep operation is lower in pLUTo-GSA than in pLUTo-BSA, the latency of the total pLUTo LUT Query is higher in pLUTo-GSA than in pLUTo-BSA.

**5.2.3. Analysis of pLUTo-GSA.** pLUTo-GSA's design entails the following pLUTo LUT Query throughput, pLUTo LUT Query energy consumption, and area overhead values:

• *Throughput:* pLUTo-GSA's maximum throughput (in *number* of LUT queries per second, LUTs/s) for a single pLUToenabled subarray depends on the number of LUT indices that fit in the source subarray ( $\frac{RowSize_{bytes}}{LUT_{ElementSize}}$ ), the latency of a pLUTo Row Sweep operation (tRCD × LUT<sub>#Elems</sub> + tRP),

<sup>&</sup>lt;sup>3</sup> The ratio between the latencies of the pLUTo Row Sweep in pLUTo-BSA and pLUTo-GSA is given by  $\frac{(\text{tRCD+tRP})\times N}{\text{tRCD}\times N + \text{tRP}}$ . Under the assumption that tRCD  $\approx$  tRP, this simplifies to  $\frac{2\times N}{1+N}$ , which approaches 2 for large values of *N*.

and the latency of loading LUT elements into the pLUToenabled subarray, since LUT elements are destroyed after each pLUTo Row Sweep ( $LISA_{RBM} \times LUT_{\#Elems}$ ). Thus, the maximum throughput achievable with pLUTo-GSA is

$$GSA_{Throughput} = \frac{RowSize_{bits}/input_{bit width}}{LISA_{RBM} \times LUT_{\#Elems} + (tRCD \times LUT_{\#Elems} + tRP)} LUTs/s.$$

• *Energy Consumption:* The energy pLUTo-GSA consumes during a pLUTo Row Sweep operation depends on the number of elements in the LUT and the energy consumed by a DRAM row activation and precharge operation:

$GSA_{Energy} = \mathsf{E}_{LISA_{RBM}} \times LUT_{\#Elems} + \mathsf{E}_{\mathsf{RCD}} \times LUT_{\#Elems} + \mathsf{E}_{\mathsf{RP}}.$

• *Area Overhead:* The area overhead of pLUTo-GSA's design includes the area of the pLUTo Match Logic (*RowSizebytes* × *AreaByteComp*), and matchline-controlled switches (*RowSizebits* × *Aream-c switch*). Thus, the total area overhead of pLUTo-GSA is

$GSA_{Area} = RowSize_{bytes} \times Area_{ByteComp} + RowSize_{bits} \times Area_{m-c \ switch}.$

# 5.3. pLUTo-GMC (Gated Memory Cell) Design

*pLUTo-GMC* provides higher throughput and energy efficiency over pLUTo-BSA, at the expense of increased area overhead. pLUTo-GMC differs from pLUTo-BSA in its DRAM cell design, pLUTo-enabled row buffer design, and pLUTo Row Sweep implementation. Similarly to pLUTo-GSA, pLUTo-GMC's key *idea* is to use the sense amplifier in the pLUTo-enabled subarray as a buffer to store the matched LUT elements during a pLUTo LUT Query (instead of adding a new buffer, as pLUTo-BSA does). However, in contrast to pLUTo-GSA, row activations during the pLUTo Row Sweep in pLUTo-GMC are not destructive, since charge is allowed to flow from the DRAM cell to the bitline only if there is a match between the row index and the LUT indices in the source subarray. To do so, pLUTo-GMC adds an extra transistor in each DRAM cell of the pLUTo-enabled subarray. As such, pLUTo-GMC is the most intrusive to the subarray design (because it changes the DRAM cell itself).

**5.3.1. pLUTo-GMC DRAM Cell.** pLUTo-GMC implements a 2T1C DRAM cell instead of the conventional 1T1C design (described in Section 2.1). An additional transistor connects the DRAM cell's access transistor to the bitline. The output of the pLUTo Match Logic (i.e., the matchline) controls the additional transistor in each cell, as shown in Figure 4c. The matchline signal thus controls whether a cell in an activated row shares charge with the bitline. This significantly reduces the overall movement of charge, since charge only flows between the DRAM cell and the bitline if the pLUTo Match Logic outputs a match during the pLUTo LUT Query operation, which reduces the overall energy consumption of pLUTo-GMCduring a pLUTo Row Sweepcompared to both pLUTo-BSA and pLUTo-GSA.

**5.3.2. pLUTo-GMC Row Buffer.** In pLUTo-GMC, additional matchline-controlled switches exist between each sense amplifier and its enable signal. The role of these switches is to ensure that, when a row is activated, the sense amplifier connected to a given DRAM cell only senses the bitline voltage if *both*

the wordline and the matchline signals are high. Without this safeguard, the sense amplifiers would be activated when cells in the active row are not connected to the bitline (i.e., when the wordline signal is high for a given row, but the matchline signals are low for one or more cells in that row), which would lead to undefined behavior. In addition, these matchline-controlled switches enable pLUTo-GMC to perform back-to-back activations without needing to precharge the subarray. This happens because, when a matchline signal is low, the corresponding bitline behaves as if it had remained inactive, which keeps it in its precharged state. Conversely, only when the matchline is high does the sense amplifier become enabled.

5.3.3. The pLUTo Row Sweep. pLUTo-GMC optimizes the pLUTo Row Sweep operation by introducing the ability to perform back-to-back activations *without* the need to precharge the bitlines. Leveraging this optimization, pLUTo-GMC outperforms pLUTo-BSA in the pLUTo Row Sweep by almost 2×.4 To achieve this optimization, pLUTo-GMC adopts the following two key design features. First, a sense amplifier is only enabled when there is a match in the corresponding pLUTo Match Logic. This means that an activation only perturbs a bitline if the associated matchline signal is high, and that the voltage in the bitlines is kept at  $V_{DD}/2$  (i.e., in the precharged state) if the matchline signal is low. Second, since each source row element necessarily only has one match in a LUT, the sense amplifier is only enabled for a single row activation during an entire pLUTo LUT Query. Therefore, we can guarantee that back-to-back row activations will not open the gating transistors of any two cells sharing the same bitline, and thus will not destroy the data in the cell. As in pLUTo-GSA, the total time required to perform a pLUTo Row Sweep in pLUTo-GMC is  $tRCD \times LUT_{\#Elems} + tRP$ . In addition, due to matchline-controlled switches (Section 5.1.3), pLUTo-GMC does not destroy the data in the LUTs; this translates into significant performance gains, as there is no need to repeatedly load LUT data into the subarray.

**5.3.4. Analysis of pLUTo-GMC.** pLUTo-GMC's design entails the following pLUTo LUT Query throughput, pLUTo LUT Query energy consumption, and area overhead values:

• *Throughput:* pLUTo-GMC's maximum throughput (in *number of LUT queries per second*, LUTs/s) for a single pLUTo-enabled subarray depends on the number of LUT indices that fit in the source subarray (*RowSizebits/inputbit width*) and the latency of a pLUTo Row Sweep operation (tRCD + tRP × *LUT*#*Elems*). Thus, the maximum throughput achievable with pLUTo-GMC is

$$GMC_{Throughput} = \frac{RowSize_{bits}/input_{bit width}}{tRCD \times LUT_{\#Elems} + tRP} LUTs/s.$$

• *Energy Consumption*: The energy pLUTo-GMC consumes during a pLUTo LUT Query operation depends on the number of elements in the LUT and the energy consumed by a DRAM row activation and precharge operation:

$$GMC_{Energy} = E_{RCD} \times LUT_{\#Elems} + E_{RP}$$

.

$<sup>^{\</sup>rm 4}$  See Footnote 3. The latency of the pLUTo Row Sweep in pLUTo-GSA and pLUTo-GMC is the same.

Area Overhead: The area overhead of pLUTo-GMC's design includes the area of the pLUTo Match Logic (*RowSize<sub>bytes</sub> × Area<sub>ByteComp</sub>*) and matchline-controlled switches (*#Rows × RowSize<sub>bits</sub> × Area<sub>m-c switch</sub>*). Thus, the total area overhead of pLUTo-GMC is

$GMC_{Area} = RowSize_{bytes} \times Area_{ByteComp} + \\ \#Rows \times RowSize_{bits} \times Area_{m-c\ switch}.$

## 5.4. Summary of pLUTo Architectures

While the pLUTo-BSA design provides a balanced trade-off between performance, energy efficiency, and area overhead, the system designer could prefer to optimize for one of these three metrics in isolation. To provide this added flexibility, we described pLUTo-GSA and pLUTo-GMC, two additional pLUTo designs with different trade-offs in performance, energy efficiency, and area overhead. Table 1 summarizes the trade-offs of each of the proposed pLUTo designs.

Table 1: Comparison of pLUTo designs' core attributes. Bold cells represent key benefits of a pLUTo design compared to others. N corresponds to LUT elements (i.e.,  $LUT_{\#Elems}$ ).

|                   | pLUTo-BSA                     | pLUTo-GSA                                             | pLUTo-GMC                               |  |

|-------------------|-------------------------------|-------------------------------------------------------|-----------------------------------------|--|

| Area Efficiency   | Medium                        | High                                                  | Low                                     |  |

| Throughput        | Medium                        | Low                                                   | High                                    |  |

| Energy Efficiency | Medium                        | Low                                                   | High                                    |  |

| Destructive Reads | No                            | Yes                                                   | No                                      |  |

| LUT Data Loading  | Once                          | After every use                                       | Once                                    |  |

| Query Latency     | $(tRCD + tRP) \times N$       | $LISA_{RBM} \times N + tRCD \times N + tRP$           | $\texttt{tRCD} \times N + \texttt{tRP}$ |  |

| Query Energy      | $(E_{RCD} + E_{RP}) \times N$ | $E_{LISA_{RBM}} \times N + E_{RCD} \times N + E_{RP}$ | $E_{RCD} \times N + E_{RP}$             |  |

Table 1 and the expressions for throughput, energy consumption and area overhead derived in Sections 5.1.4, 5.2.3 and 5.3.4 enable three key observations. First, pLUTo-GMC provides the highest throughput of the three designs  $(GMC_{Throughput} >$  $BSA_{Throughput} > GSA_{Throughput}$ ). pLUTo-GMC achieves this by 1) eliminating the need to issue PRE commands following every row activation in the pLUTo-enabled subarray (as in pLUTo-BSA), and 2) eliminating the need to load all LUT elements before each pLUTo LUT Query operation (as required by pLUTo-GSA, due to the destructive row activations required by its pLUTo Row Sweep operation). Second, GMC provides the highest energy efficiency of the three designs  $(GMC_{Energy} < BSA_{Energy} < GSA_{Energy})$ . pLUTo-GMC achieves this by 1) eliminating the energy overhead associated with the issuance of PRE commands following every row activation in the pLUTo-enabled subarray (as in pLUTo-BSA), and 2) eliminating the energy overhead associated with loading the LUTs before each pLUTo LUT Query (as in pLUTo-GSA). Third, GSA incurs the smallest area overhead of the three designs (GSA<sub>Area</sub> < BSA<sub>Area</sub> < GMC<sub>Area</sub>). pLUTo-GSA's area overhead is minimized by making as few modifications to the DRAM array as possible. In particular, pLUTo-GSA does not employ the logic components required for the operation of pLUTo-BSA (i.e., the FF buffer) or pLUTo-GMC (i.e., per-cell matchlinecontrolled switches).

We conclude that pLUTo-GSA is the most well-suited design to minimize area overhead, pLUTo-GMC is the most well-suited design to maximize either performance or energy efficiency, and pLUTo-BSA provides a trade-off point that offers intermediate throughput, energy efficiency, and area overhead metrics.

#### 5.5. Subarray-Level Parallelism

Since the lookup operations of different input values are independent of one another, many pLUTo LUT Queriescan be executed simultaneously across *multiple* subarrays by exploiting *subarray-level parallelism* (SALP) [100], as described in Section 2.2. Two important use cases benefit from the distribution of LUT queries across multiple subarrays: 1) LUT query input vectors with a very large number of LUT indices can be partitioned across multiple source subarrays to be queried simultaneously; and 2) independent pLUTo LUT Queries (possibly belonging to different threads or applications) can be executed concurrently.

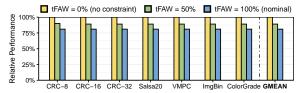

The achievable degree of subarray-level parallelism is limited by the tFAW DRAM timing constant [109, 110], which corresponds to the duration of the time window during which *at most four* ACT commands can be issued, per DRAM rank. This constraint protects against the deterioration of the DRAM reference voltage, although DRAM manufacturers have been able to mitigate it substantially in commodity DRAM chips in recent years [114], as well as to perform a targeted reduction of this parameter specifically for PiM architectures where it becomes a performance bottleneck [115]. These advances suggest that this parameter may not limit pLUTo's scalability severely.

## 5.6. Limitations of pLUTo's Subarray Design

For a single-subarray pLUTo LUT Query, the number of LUT elements can scale up to *the number of rows in the subarray.* To query LUTs with a greater number of elements, it is possible to partition a pLUTo LUT Query across subarrays. Note that partitioning the query *does not increase* latency (since multiple subarrays operate simultaneously), but *does increase* energy consumption *N*-fold, for a pLUTo LUT Query distributed across *N* subarrays. For this reason, the design of pLUTo is not well suited for executing large-bit-width lookup queries. We leave the potential exploration of alternative designs that address this limitation for future work.

# 5.7. The Role of pLUTo in the PiM Landscape

As discussed in Section 1, PnM and PuM are complementary approaches: the former enables flexible substrates that support a diverse range of operations, while the latter yields maximal performance and energy efficiency benefits. pLUTo does *not* aim to replace prior PuM proposals. Instead, it addresses an important gap in the literature and enables PuM to support more complex operations, as many applications require. Ideally, a real-world PiM system would combine the strengths of different proposals: for example, relying on SIMDRAM [75] for addition, pLUTo for trigonometric functions and bit counting operations, and near-memory general-purpose cores [67] for serial reduction and other irregular tasks. Mapping application segments to their most suitable PiM substrates is a rich area for future work.

# 6. System Integration

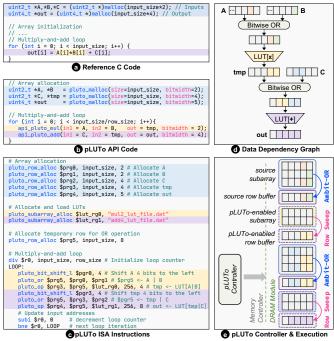

This section describes the system integration stack that enables pLUTo to operate seamlessly with the host system. There are four key components in this stack: 1) the pLUTo ISA (Section 6.1), a set of instructions that express i) pLUTo Row Sweep operations (pluto\_op), ii) bitwise logic operations [84], iii) bit- and byte-level shifting operations [79], and iv) data movement operations involving multiple DRAM rows [108]; 2) the pLUTo library (Section 6.2), a set of routines that implement complex operations (i.e., operations that involve several pLUTo ISA instructions); 3) the pLUTo Compiler (Section 6.3), which analyzes data dependences (necessary for data allocation and alignment) and translates pLUTo library routines to pLUTo ISA instructions; 4) the pLUTo Controller (Section 6.4), a modified DRAM controller that supports the execution of pLUTo ISA instructions (i.e., given a pluto\_op, the pLUTo Controller carries out the corresponding pLUTo Row Sweep operation through a series of ACT and PRE DRAM commands). The description of the entire system integration stack is depicted by Figure 5, which shows an end-to-end example of pLUTo's operation, from reference C code (a) to in-memory computation (e). This example describes the implementation of the multiply-andadd  $(A \odot B + C)$  operation between three vectors: Row A (2-bit elements), Row B (2-bit elements), and Row C (4-bit elements). Section 6.5 describes the methods of creating the LUTs used in pLUTo LUT Queries. Finally, Section 6.6 discusses the limitations of our proposed system integration of pLUTo and how we can mitigate these limitations.

Figure 5: pLUTo's system integration stack. An example is shown for the C code displayed in a. Subsequent steps are shown in topdown, left-to-right order: b implementation using pLUTo's API Library, c the transformation of the pLUTo API code performed by the pLUTo Compiler, d data dependency graph analysis, c the role of the pLUTo Controller and in-memory execution.

# 6.1. The pLUTo ISA

We propose ISA extension instructions that express the operations required by pLUTo to perform in-memory computation. The instructions in the pLUTo ISA manipulate special-purpose *pLUTo registers* that keep track of the currently allocated pLUTo data structures. We describe ISA instructions for 1) allocating memory, 2) querying LUTs (the pluto\_op), and 3) manipulating data (in-memory bitwise logic [84], bit shifting [79], and data copy [108] operations), as summarized in Table 2. Figure 5 © shows the translation of instructions from the reference program (a) into a sequence of pLUTo ISA instructions.

| Table 2: Summa | ary of pLUTo ISA extension | instructions. |

|----------------|----------------------------|---------------|

| Onenation      | Instruction                | Duonocod      |

| Operation                        | Instruction                                                                         | Proposed in            |

|----------------------------------|-------------------------------------------------------------------------------------|------------------------|

| pLUTo<br>Register Allocation     | pluto_row_alloc dst, size, bitwidth<br>pluto_subarray_alloc dst, num_rows, lut_file | This work<br>This work |

| pLUTo<br>Row Sweep               | <pre>pluto_op dst, src, lut_subarr, lut_size, lut_bitw</pre>                        | This work              |

| Bitwise<br>Logic Operations      | pluto_{not, and, or} dst, src1, scr2                                                | [84]                   |

| Bit- and Byte-<br>Level Shifting | pluto_bit_{shift_l, shift_r} src, #N<br>pluto_byte_{shift_l, shift_r} src, #N       | [79]<br>[79]           |

| In-DRAM<br>Data Movement         | pluto_move dst, src                                                                 | [108]                  |

pLUTo Registers. pLUTo's instructions operate at the granularity of contiguously allocated DRAM rows (for both LUT query input and output vectors) and contiguously allocated DRAM subarrays (pLUTo-enabled subarrays that hold LUTs). To guarantee that the physical memory addresses of all DRAM rows involved in a pLUTo LUT Query operation are contiguously allocated in the DRAM array, we define two data structures (row registers and subarray registers) that separately capture these two abstractions. Each pLUTo Row Register is a special-purpose architectural register that identifies a DRAM row to be used either as the input or the output of a pLUTo LUT Query. Each pLUTo Subarray Register is a special-purpose architectural register that identifies a LUT-holding DRAM subarray to be used in a pLUTo LUT Query. These two types of registers are used as arguments of pLUTo's ISA instructions where appropriate. The allocation of pLUTo Registers is performed by the operating system via a call to a pLUTo allocation routine (see "Memory Allocation", Section 6.1). The allocation of both register types is recorded in an in-memory allocation table, which the pLUTo Controller (Section 6.4) accesses to derive the physical memory addresses required to issue DRAM commands during the execution of pLUTo LUT Queries.

**Memory Allocation.** We introduce two instructions to enable the compiler or the programmer to allocate pLUTo Registers. The first instruction, pluto\_row\_alloc, allocates the memory space (as a *whole number* of memory rows) to be used by a source or destination row involved in the execution of pLUTo ISA instructions. This instruction has two inputs (size and bitwidth) and one output (dst). It sets dst to a valid pLUTo Row Register that is used to reference the allocated size-byte memory row(s) whose elements are bitwidth-bits wide. bitwidth is only a meaningful parameter for data structures used as *inputs*, and is equal to log<sub>2</sub>(lut\_size), where lut\_size is number of elements in the LUT to query. The second instruction, pluto\_subarray\_alloc, allocates memory space corresponding to consecutive rows belonging to a single subarray, in which the LUT required by a pluto\_op will be stored. This instruction has two inputs (num\_rows and lut\_file) and one output (dst). It sets dst to a valid pointer that references the allocated DRAM subarray. num\_rows is the number of rows to be reserved, i.e., the number of elements in the associated LUT, and lut\_file is a memory location that holds the LUT data to be stored in the allocated subarray.

**LUT Querying.** A pLUTo LUT Query (Section 4.1) uniquely maps to a pluto\_op instruction, which has three inputs (src, lut\_subarr, lut\_size, and lut\_bitw) and one output (dst). Here, dst and src are the pLUTo Row Registers of the destination and source rows. lut\_subarr is the physical address of the pLUTo-enabled subarray where the LUT to query is stored. lut\_size is the number of LUT elements, i.e., the number of rows to sweep. lut\_size must be a power of two: more specifically,  $lut_size := 2^N$ , where N is the bit width of each source row value; for example, a 4-bit-input LUT contains  $2^4 = 16$ elements, and thus requires the sweeping of 16 rows. lut\_bitw specifies the bit width of the LUT elements,<sup>5</sup> i.e., the width of the match logic's comparators for this pluto\_op. A pluto\_op instruction always operates at the granularity of a DRAM row; as a result, operating on S input bytes requires  $\left[\frac{S}{DRAM_{row size}}\right]$ pluto\_op instructions.

**Bit Manipulation.** pLUTo requires bit manipulation operations proposed by prior works [79, 84, 108], as shown in Table 2. We use these operations to align source row values (bit shifting using pluto\_bit\_\* and pluto\_byte\_\*), merge operands between source rows (bitwise OR using pluto\_or), apply bit masks to input and output rows (bitwise AND using pluto\_and), and copy rows in-memory (row buffer to row buffer data copy using pluto\_move).

#### 6.2. The pLUTo Library

The pLUTo library encompasses 1) *computation* routines, which the programmer may conveniently use to express operations at a high level of abstraction, and 2) a routine for *memory allocation* (pluto\_alloc), which the programmer may use to instantiate the data structures involved in pLUTo's operation (i.e., the source and destination rows and the LUT-holding subarrays).

**Computation.** Examples of pLUToLibrary computation routines include common operations (e.g., api\_pluto\_add and api\_pluto\_mul express addition and multiplication). Figure 5 **b** contains a code example with pLUTo library calls (api\_pluto\_add, api\_pluto\_mul) in place of the addition and multiplication operations in the reference code (Figure 5 **a**). Each of the routines in the pLUTo library translates into a predetermined, constant sequence of pLUTo ISA instructions. For example, the 4-bit addition operation

api\_pluto\_add(in1,in2,out,bitwidth=4)

*always* corresponds to the following sequence of pLUTo ISA instructions:

#### pluto\_or temp,in1,in2

pluto\_op dst,temp,add4\_lut,lut\_size=256,lut\_bitw=8 Here, dst denotes the destination row to which the result will be stored, temp holds the result of the bitwise OR operation that combines the two source rows, add4\_lut denotes the subarray that holds the LUT with the results for the 4-bit addition, and lut\_size and lut\_bitw are uniquely determined by the bit width of this operation (256 and 8, respectively, in this example). pLUTo library routines always assume a specific data alignment (e.g., the pluto\_add operation assumes that the left and right operands are concatenated before performing the LUT query). However, these routines *do not explicitly guarantee this alignment;* instead, the responsibility of ensuring correct input operand alignment is assumed by the pLUTo Compiler, as explained in Section 6.3.

**Memory Allocation.** To abstract the low-level memory allocation instructions defined in Section 6.1, the pLUTo Library implements the pluto\_malloc routine, defined as pluto\_malloc(size,bitwidth). Here, size is the number of bits to be allocated, and bitwidth is the bit width of each element (either an input/output value, or a LUT element). Based on the dependences between the arguments of this function, the pLUTo Compiler (Section 6.3) is able to infer a sequence of pLUTo ISA instructions (i.e., pluto\_row\_alloc, pluto\_subarray\_alloc) that are equivalent to it. and in Figure 5 show an example of this compilation process.

#### 6.3. The pLUTo Compiler

The role of the pLUTo Compiler is to identify the dependences between operands used by pLUTo library routines to ensure the correct allocation (i.e., pluto\_alloc\_\*) and alignment of these operands. The compiler may achieve operand alignment by inserting additional pLUTo ISA instructions to perform bit shifting (pluto\_{bit,byte}\_\*), bit masking (pluto\_and), and row merging (pluto\_or) operations as needed, in addition to the pLUTo ISA instructions specified by each pLUToLibrary routine. As an example of the role of the compiler, consider the multiplication between the 2-bit elements of arrays A and B using the api\_pluto\_mul instruction, as shown in Figure 5 C. The translation from the api\_pluto\_mul call to pLUTo ISA instructions yields only a pluto\_or and a pluto\_op, and therefore does not guarantee that each value from A is combined with its counterpart from B to create the value to be queried in the LUT. In this example, the compiler guarantees correct operand alignment by performing the operations shown in **(d)**, namely 1) shifting the contents of input row A to the left by two bits, and 2) merging the result of operation 1) with input row B using a bitwise OR.

# 6.4. The pLUTo Controller

The pLUTo Controller, which extends the DRAM controller, executes the pLUTo ISA instructions that are either 1) specified by the programmer using pLUTo Library routines, or 2) inserted by the pLUTo Compiler to ensure correct operand alignment. Each

<sup>&</sup>lt;sup>5</sup> lut\_bitw can only be greater than or equal to *N*. If  $lut_bitw > N$ , the source row values will be zero-padded: as an example, for N = 1 and  $lut_bitw = 8$ , the 1-bit values {0, 1} would be zero-padded to a width of 8 bits (i.e., {00000000, 00000001}) and used to query a 2-entry LUT whose elements may be any 8-bit value (e.g., {00000000, 1111111}).

of these ISA instructions translates into either i) a predefined sequence of ACT and PRE commands, which the pLUTo Controller stores in an internal ROM (for the execution of bitwise logic operations, bit- and byte-level shifting, and in-DRAM data movement operations); or ii) a pLUTo Row Sweep command.

The pLUTo Controller's hardware consists of: 1) a small internal ROM that maps each pLUTo ISA instruction to appropriate DRAM commands; 2) a small register file that holds pLUTo Row Registers; and 3) a finite state machine that decodes pLUTo ISA instructions, gathers the physical addresses of all operands of a pLUTo ISA instruction and controls the execution flow of pLUTo's in-memory operations. The hardware and operation of the pLUTo Controller resemble those of SIMDRAM's Control Unit [75], and thus incur negligible area overhead on the host CPU die (< 0.08%).

# 6.5. Loading LUT Data

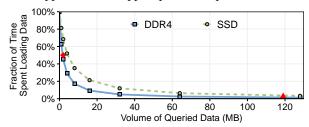

To load the LUTs required by pLUTo LUT Queries, it is necessary to 1) *allocate LUT subarrays* (using the pluto\_subarray\_alloc operation) that are adjacent or in close physical proximity to the source and destination rows, and 2) *load the LUTs* into these subarrays. The loading of LUTs may take place in one of three ways, which we quantitatively compare in Section 8.5:

**1. First-Time Generation.** The first time a LUT is required, its elements must be computed from scratch. Optionally, these values may then be saved in memory for later reuse. This procedure is similar to operand memoization [116] and presents an opportunity for potential further optimizations, as described in prior works [116–120]. We leave the exploration of more complex memoization strategies for future work.

**2. Loading From Memory.** If a LUT already exists in memory, the most efficient way to reuse it is by copying it to the designated pLUTo-enabled subarray using LISA-RBM [108] (if the source and destination subarrays are in close physical proximity) or a CPU-mediated copy operation.

**3. Loading From Secondary Storage.** If a LUT is stored in secondary storage (e.g., at compile time, or following First-Time Generation), it may be loaded into the main memory at runtime using a direct memory access (DMA) operation.

#### 6.6. Limitations of the System Integration Stack

Address Translation. Ensuring the physical proximity between the source row, the LUT-holding subarray, and the destination row requires knowledge of the physical address mapping of the involved DRAM subarrays, banks, and ranks. Two possible approaches to achieve this are 1) via the help of a memory controller that can provide this information, and 2) via an *a priori* reverse-engineering effort that allows the memory mapping scheme to be recovered [121].

**Coherence.** pLUTo does *not* provide means to enforce coherence between the data stored in pLUTo subarrays and the data stored in other locations in the system (e.g., CPU caches). For this reason, programmers are responsible for preventing data decoherence stemming from modifications by simultaneous CPU and pLUTo operations (e.g., using instructions to flush cache

lines belonging to memory addresses that pLUTo will operate on). pLUTo can leverage coherence optimizations tailored to PiM to improve overall performance [32, 48, 122].

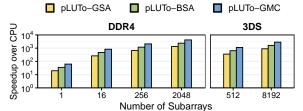

# 7. Methodology

We evaluate the three proposed pLUTo designs: pLUTo-GSA, pLUTo-BSA, and pLUTo-GMC. Unless stated otherwise, our implementations assume the parallel operation of 16 subarrays with 8 kB row buffers for DDR4 memory [100], and 512 subarrays with 256 B row buffers for 3D-stacked (3DS) [65] memory. These two design points are comparable since the volume of data processed *per operation* is identical in both cases:  $16 \times 8 \ kB = 512 \times 256 \ B = 128 \ kB$ . We compare each pLUTodesign against four baselines: 1) a state-of-the-art CPU, 2) a state-of-the-art GPU, 3) a simulated Processing-near-Memory (PnM) accelerator, and 4) a simulated FPGA. Table 3 shows the main parameters we use in our evaluations.

Table 3: Configuration of the simulated system.

| Parameter   | Configuration                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Memory | DDR4 2400 MHz, 8 GB, 1-channel, 1-rank, 4-bank<br>groups, 4-banks per bank group, 512 rows per subar-<br>ray, 8 kB per row; timings 17-17-17 (14.16 ns) |

| PnM         | HMC Model [67] with support for bitwise opera-<br>tions [84] and bit shifting [79]; on-die core with<br>1.25 GHz clock, 10 W TDP                        |

| FPGA        | Zynq® UltraScale+ MPSoC ZCU102 [105]                                                                                                                    |

| pLUTo       | 16-subarray parallelism [100] unless stated otherwise;<br>unthrottled rate of row activations (tFAW = 0s)                                               |

#### 7.1. Evaluation Frameworks

**Baselines.** We evaluated the CPU and GPU baselines on a real system equipped with an Intel® Xeon Gold 5118 [103] CPU and an NVIDIA® GeForce RTX 3080 Ti [104] GPU. The CPU versions of our evaluated workloads employ SSE2 and SSE4 Intel® Streaming SIMD Extensions. We evaluate the FPGA baseline using high-level synthesis (HLS) implementations created with Vitis 2020.1 [123] and Vivado 2020.1 [124], and perform post-synthesis simulation for a Xilinx Zynq UltraScale ZCU102 FPGA [105]. For the evaluation of the PnM baseline, we simulate an HMC-based system [67] with support for bulk bitwise operations as described in Ambit [84] and bit shifting as described in DRISA [79]. We simulate various configurations of pLUToon DDR4 [110] and HMC [67] memory models using a custom-built simulator, which we have made publicly available at [125, 126] under an open-source license.

**pLUTo.** Our simulator estimates the performance of pLUTo operations by parsing the sequence of memory commands required to perform them and enforcing the memory's timing parameters. The simulator then outputs the total time elapsed and energy consumed to complete the operations.

**Energy and Area.** We evaluate the energy consumption and area overhead of pLUTo configurations using CACTI 7 [127] DDR4 and HMC models. These models supply the energy consumption of each memory command and the area of each memory component. Using these values, we extrapolate pLUTo's

energy consumption and area overhead by considering the transistor count associated with the logic required to implement its functionality, including 1) the addition of the match logic, 2) modifications to the subarray architecture and memory controller, and 3) the addition of the pLUTo controller.

#### 7.2. Workloads

Table 4 shows the names and characteristics of the workloads we evaluate. We select these workloads because 1) they exemplify general-purpose, real-world functions that cannot be efficiently executed by previous Processing-using-Memory architectures [75, 84] (e.g., substitution tables [128, 129], polynomial division [130]), 2) they include segments that are well-suited for LUT-based computation, and 3) their typical working sets are much larger than the cache size of modern systems.

| Name                                    | Parameters                      |  |  |  |

|-----------------------------------------|---------------------------------|--|--|--|

| Vector Addition, LUT-based [131]        | Element width: 4 bits           |  |  |  |

| Vector Point-Wise Multiplication [131]  | Q Format: Q1.7, Q1.15           |  |  |  |

| Row-Level Bitwise Logic Operations [84] | # LUT entries: 4                |  |  |  |

| Bit Counting [130]                      | BC-4: 4 bits, 16-entry LUT; BC- |  |  |  |

| Bit Counting [150]                      | 8: 8 bits, 256-entry LUT        |  |  |  |

| CRC-8/16/32 [130]                       | Packet size: 128 B              |  |  |  |

| Salsa20 [128], VMPC [129]               | Packet size: 512 B              |  |  |  |

| Imaga Binarization (ImgBin) [122]       | 3-channel 8-bit image, 936000   |  |  |  |

| Image Binarization (ImgBin) [132]       | pixels; threshold: 50%          |  |  |  |

| Color Grading (ColorGrada) [122]        | One 3-channel 8-bit image,      |  |  |  |

| Color Grading (ColorGrade) [133]        | 936000 pixels; 8-bit to 8-bit   |  |  |  |

# 8. Evaluation

In this section, we evaluate pLUTo's reliable and correct operation (Section 8.1), performance (Section 8.2), energy consumption (Section 8.3), and area overhead (Section 8.4). We also carry out performance sensitivity analyses to assess the cost of loading LUTs (Section 8.5), the scalability of pLUTo (Section 8.6), tFAW's impact on performance (Section 8.7), and the effect of varying degrees of subarray-level parallelism (Section 8.8). Finally, we discuss how pLUTo compares to various prior approaches (Section 8.9).

#### 8.1. Reliability and Correctness

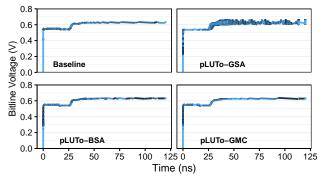

We perform circuit-level SPICE simulations to verify that the modifications required by each of the three pLUTo designs do not compromise the correct and reliable operation of DRAM. We model the effect of activating a DRAM row in unmodified DRAM and in each of the three designs of pLUTo. We model DRAM cells based on Low-Power 22nm Metal Gate PTM transistors [134], and conduct Monte Carlo simulations of 100 runs, where the process variation is assumed to be 5%. Figure 6 shows the results of these simulations. Our results show that the proposed changes in each of the three pLUTo designs *do not introduce* errors in DRAM operation. The observed disturbances in the final bitline voltage following a row activation correspond to only 0.9% of the reference voltage value.

We make three key observations. First, the correctness of the row activation is not affected in any of the proposed designs, since the bitline voltage reaches the value required to

Figure 6: Bitline voltage level over time in response to wordline activation at time = 0. Shades of blue indicate different runs of our Monte Carlo simulation.

trigger the activation in all cases. Second, in all pLUTo designs, the activation time is *not* affected by the introduced DRAM modifications. Third, the activation procedure is the noisiest for pLUTo-GSA. This is expected due to the operational principles of pLUTo-GSA (Section 5.2), whereby the contents of DRAM cells in consecutive rows are shared with the bitline *without* precharging the array after each activation until the end of the pLUTo Row Sweep. However, we observe correct row activation behavior even in this case.

#### 8.2. Performance

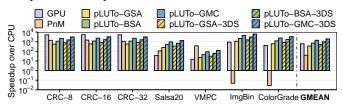

Figure 7 shows the performance of GPU, PnM, and pLUTo systems, normalized to the baseline CPU. For the DDR4 (3DS) implementation, the performance of pLUTo-GSA, pLUTo-BSA, and pLUTo-GMCmechanisms, on average across all workloads, is  $357 \times /0.6 \times /9.2 \times (496 \times /0.8 \times /12.7 \times)$ ,  $713 \times /1.2 \times /18.3 \times (990 \times /1.6 \times /25.4 \times)$ , and  $1413 \times /2.3 \times /36.2 \times$ (1962×/3.2×/50.3×) that of the CPU/GPU/PnM baselines, respectively. All pLUTo designs achieve performance comparable to or higher than that of the GPU, and consistently outperform the PnM baseline. We make two key observations. First, the 3DS-based pLUTo designs consistently outperform their DDR4 counterparts by 38% on average across the three pLUTo designs. This is due to HMC's faster row activations, which lead to faster pLUTo LUT Queries. Second, the CRC workloads show the smallest overall benefit from execution in pLUTo. The speedup in these workloads is bottlenecked by a serial reduction step, which must be performed in the CPU (pLUTo-DDR4) or in the logic layer of HMC (pLUTo-3DS). Nevertheless, the acceleration of the parallel portion of the CRC workloads still allows most pLUTo designs to achieve performance comparable to or higher than that of the GPU. We conclude that pLUTosignificantly improves the performance of a variety of workloads compared to both processor-centric and PnM architectures.

Figure 7: Speedup of GPU, PnM, and pLUTo relative to the baseline CPU. The y-axis uses a logarithmic scale; higher is better.

8.2.1. Performance per Area. Figure 8 shows the speedup per unit area of GPU and pLUTo systems, normalized to the baseline CPU. The area overhead of pLUTo-3DS designs is calculated assuming an area overhead of 4.4  $mm^2$  per vault [11, 48, 67]. For the DDR4 (3DS) implementation, the performance per unit area of pLUTo-GSA, pLUTo-BSA, and pLUTo-GMC mechanisms, on average across all workloads, is  $426 \times /441 \times (12405 \times /12856 \times), 801 \times /830 \times (24747 \times /25646 \times),$ and 1504×/1558× (39245×/40670×) that of the CPU/GPU baselines, respectively. We make three key observations. First, all pLUTo designs provide substantially higher performance per unit area than both the CPU and the GPU ( $4283 \times$  and  $2577 \times$ , respectively, on average across all pLUTo designs), and consistently outperform both baselines by a wide margin. This improvement is considerably greater than the one observed when considering performance in isolation (Section 8.2) and highlights the potential benefits of scaling pLUTo's design further with larger DRAM systems. Second, pLUTo-3DS designs are more area-efficient than their DDR4 counterparts across all workloads. This is a consequence of the large available area and 3D density in the HMC substrate. Third, we observe pLUTo's greatest improvements in Salsa20 and VMPC (respectively 2970×/50591× and 273×/106151× the performance per unit area of the CPU/GPU, on average across all pLUTo designs). These workloads are very memory-intensive, and are therefore well-suited for in-memory execution. In contrast, for the Salsa20 and VMPC workloads, the GPU baseline provides performance per unit area results that fall below even those of the baseline CPU, which highlights the negative impact of data movement bottlenecks in the execution of memory-intensive workloads under a processor-centric computing paradigm.

Figure 8: Speedup of GPU and pLUTo relative to CPU, normalized to area. The y-axis uses a logarithmic scale; higher is better.

8.2.2. Comparison with FPGA. Figure 9 shows the performance of the evaluated pLUTo systems normalized to the baseline FPGA. We observe that pLUTo outperforms the FPGA baseline across all workloads we evaluate. For the DDR4 (3DS) implementation, the performance of pLUTo-GSA, pLUTo-BSA, and pLUTo-GMC mechanisms, on average across all workloads, is  $160 \times (111 \times)$ ,  $274 \times (190 \times)$ , and  $459 \times (318 \times)$  that of the FPGA baseline, respectively. The most significant gains are associated with workloads that rely on smaller LUTs (e.g., BC4, ImgBin), and the smallest gains correspond to operations with large input bit widths (e.g., MUL16). We conclude that, although both the FPGA and pLUTo rely on LUT-based computation, the former's access to data in memory is still limited by main memory bandwidth. In contrast, pLUTo exploits much higher main memory bandwidth via the pLUTo LUT Query, leading to overall higher performance.

Figure 9: pLUTo speedup relative to the baseline FPGA. The yaxis uses a logarithmic scale; higher is better.

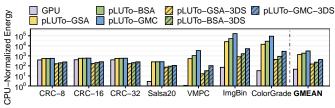

#### 8.3. Energy Consumption

Figure 10 shows the energy consumed by the GPU and pLUTo systems when executing the evaluated workloads, normalized to the baseline CPU. pLUTo's energy consumption depends on the total number of DRAM operations required by the executed pLUTo ISA instructions (Table 2), and therefore *does not vary with different degrees of subarray-level parallelism.* For the DDR4 (3DS) implementation, pLUTo-GSA, pLUTo-BSA, and pLUTo-GMC systems, on average across all workloads, consume  $1361.7 \times /29 \times (154.3 \times /3.3 \times) 1855 \times /39.5 \times (235.8 \times /5 \times) 3071.4 \times /65.3 \times (430.8 \times /9.2 \times)$  less energy than the CPU/GPU baselines, respectively.

We make two key observations. First, the energy savings enabled by pLUTo are considerably greater in workloads that are especially memory-intensive (e.g., VMPC) or require simple operations (e.g., ImgBin), but becomes lower as workload complexity increases (e.g., CRC-8/16/32). This trend is consistent with our observations from Section 8.2.1. Second, in some of the workloads (e.g., CRC-8/16/32, Salsa20), the energy consumption values of all three pLUTo designs are similar to each other. This is due to the relatively small number of pLUTo Row Sweep operations required to execute these workloads, which are not enough to highlight the differences in energy consumption of each pLUTo design. As a result, the overall impact of the improved efficiency of the pLUTo Row Sweep in pLUTo-BSA and pLUTo-GMC relative to pLUTo-GSA becomes less pronounced. We conclude that pLUTosignificantly reduces energy consumption compared to processor-centric architectures for various workloads.

Figure 10: Energy consumption of GPU and pLUTo compared to the CPU. The y-axis uses a logarithmic scale; higher is better.

#### 8.4. Area Overhead

Table 5 shows the estimated area of the baseline DRAM and three pLUTo designs, broken down by DRAM component. These estimates are derived from transistor count estimates and rely on the DRAM area models provided by CACTI 7 [127].

**pLUTo-GSA.** The estimated area overhead of the matchlinecontrolled switch (shown in Figure 4b) is 20% of the area of a sense amplifier per bitline. The total area overhead of pLUTo-GSA is 10.2% of the DRAM chip area. **pLUTo-BSA.** The estimated area overhead of the matchlinecontrolled switch and the FF (shown in Figure 4a) is 60% of the area taken up by sense amplifiers in the base DRAM chip. The total area overhead of pLUTo-BSA is 16.7% of the DRAM chip area.

**pLUTo-GMC.** The estimated area overhead of the matchlinecontrolled switch per 2T1C DRAM cell (shown in Figure 4c) is 25%. The total area overhead of pLUTo-GMC is 23.1% of the DRAM chip area.

Table 5: Area breakdown for DRAM and the three pLUTo designs.

|          |                 | Base DRAM | pLUTo-GSA | pLUTo-BSA | pLUTo-GMC |